Az IBM elkészítette a világ elsõ 2 nm-es chipjét

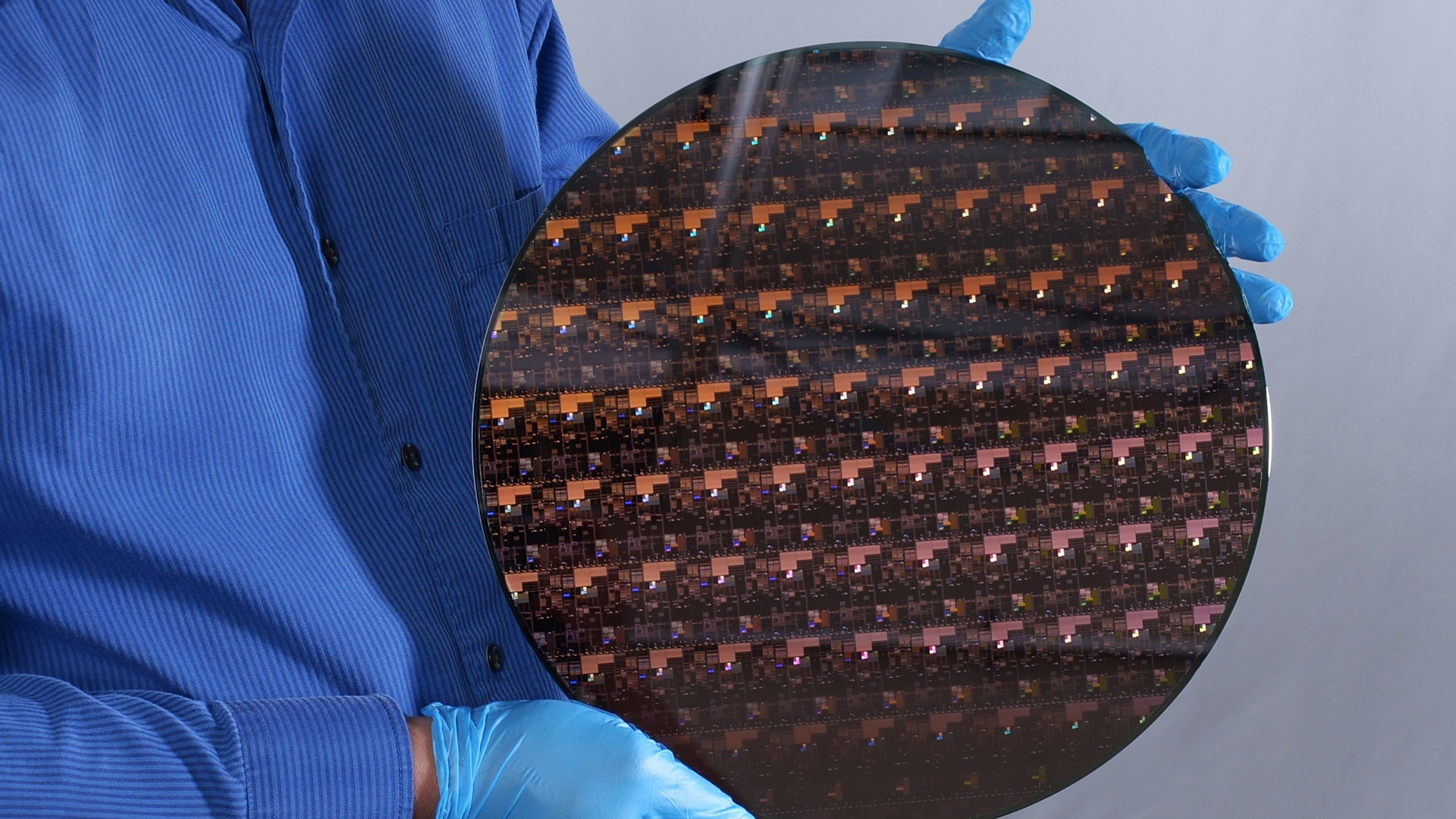

A semmibõl érkezett bejelentés szerint újdonságuk sokkal hatékonyabb, mint az ismert 7 nm-es eljárások![]()

Sokan Gordon Moore, az Intel egyik alapítójának törvényét emlegették, miután találkoztak az IBM friss bejelentésével, melyben leplezték a világ elsõ két 2 nm-es eljárással készült chipjeit. Úgy tûnik, hogy a félvezetõipar most egy újabb lépéssel kerülhet közelebb a jövõhöz, hiszen nem is olyan hosszú idõ múlva az új apróságok beköltözhetnek az okostelefonok, laptopok és más digitális eszközök burkolata alá.

Néhány évvel ezelõtt még számos számítógép vagy laptop burkolatán díszelgett az ismerõs IBM logó, ám az, hogy ma már ritkábban találkozhatunk a nevükkel, az távolról sem jelenti azt, hogy a veterán vállalat valóban a háttérbe szorult volna. Az IBM a világ egyik vezetõ kutatóközpontja a jövõbeli félvezetõ-technológiák terén, és annak ellenére, hogy nincsenek saját gyártóparkjaik, az IBM másokkal együttmûködve fejleszt gyártásra váró szellemi tulajdont. Erre jó példa ez a hír is, hiszen a hardver- és szoftverfejlesztéssel egyaránt foglalatoskodó cég most egy olyan szabadalommal állhatott elõ, mely valóban fejlettebb lehet, mint bármi, amit jelenleg a chipgyártásban alkalmaznak. A nanométerek emlegetése sokaknak kifejezetten megtévesztõ lehet, és idõnként a cégek képviselõi és mérnökei is megjegyzik, hogy ezeket a számokat nem feltétlenül kell szó szerint érteni. Például az is megeshet, hogy két konkurens cég fejlesztése elõtt eltérõ szám szerepel, de valójában teljesítmény és hatékonyság szempontjából is közel egyenértékûek. Amire ezúttal is figyelnünk kell, az a tranzisztorszám, ugyanis mostantól drasztikusan megnõhet az egyetlen chipre levetített tranzisztorsûrûség.

Ha az IBM ígéretei valósak, új 2 nm-es fejlesztésük a jelenleg is elterjedt 7 nm-es lapkákhoz képest 45 %-kal több teljesítményt szabadíthat fel, míg az eközben felhasznált energia 75 %-kal lehet kevesebb. Az AnandTech cikkében négyzetmilliméterenként 333 millió tranzisztorról olvashatunk (MTr/mm2), amit, ha összehasonlítunk a TSMC legfejlettebb 5 nm-es megoldásaival, akkor ott 173 milliót tranzisztor jut egy négyzetmilliméterre, míg a Samsung 5 nm-es gyártósorain 127 millió. A drámaian nagy ugrás egyetlen szépséghibája, hogy a bemutatott szilíciumostya és az aprócska chip egyelõre csak a fejlesztés sikerét bizonyítja, a valós termékek gyártásától sajnos még évekre lehetünk. Ez igazán izgalmas versenyt eredményezhet, hiszen a TSMC idén már kísérleti gyártás alá vonná 3nm-es eljárását, jövõ év végén pedig akár be is vezethetné, mely saját 5nm-es eljárásához képest 1.7-szeres tranzisztorsûrûséget, 27 %-kal jobb fogyasztást és 11 %-os teljesítménynövekedést ígér.

Az egészen minimális helyre milliárdszám bezsúfolt tranzisztorok, az IBM esetében a Gate All Around FET (GAAFET), avagy nanohuzalos technológia segítségével valósultak meg, melyre a TSMC 2 nm-en, a Samsung pedig 3 nm-en áll át, de szóba került az Intel is, aki 5 nm-en vetheti be a technológiát, amennyiben egyszer elér odáig. Utóbbinak amúgy kapóra jöhet az IBM-mel közös munka, hiszen az IBM a Samsung mellett velük is együttmûködik. A friss fejlesztések és technológiák némelyike az Intelnél is nagyban segítheti az elõrelépést, bár attól egyelõre nem kell tartanunk, hogy egyhamar elõrukkolnak 2 nm-es gyártásra tervezett processzorokkal, hiszen esetükben még a 7 nm is egy megmászásra váró létra. Az iparnak mindenesetre jót tesznek az ilyen húzások, hiszen 2017-ben még 5 nm-rõl és 30 milliárd tranzisztorról hallhattunk, most meg útban a 2 nm, mely az IBM szerint „50 milliárd tranzisztort tud egy köröm nagyságú chipbe" zsúfolni.

Kíváncsian várjuk, hogy mikor csiszolják tökéletesre a fejlesztést, és hogy melyik gyártó eszközeiben találkozhatunk velük elõször, ami most fõleg azért kérdéses, hiszen a jelenlegi félvezetõhiány miatt még a kidolgozott eljárásokat sem vethetik be teljes kihasználtság mellett.

Processzor választás – Teljes útmutató CPU választáshoz

Amikor egy számítógépre gondolsz, könnyű a látványos elemekre fókuszálni: videókártya, tárhely vagy dizájn. A processzor ezzel szemben láthatatlanul dolgozik – mégis minden művelet rajta keresztül történik.

A CPU a rendszer működésének központja. Minden kattintás, minden program, minden számítás itt válik végrehajtható utasítássá. Ez határozza meg, mennyire gyorsan reagál a gép, mennyire stabil több feladat párhuzamos futtatásakor, és mennyire „folyékony” a használati élmény.

Ezért a processzorválasztás nem egyszerűen specifikációs kérdés, hanem működési modell választás. Ha itt rossz döntés születik, azt nem egyetlen helyzetben, hanem folyamatosan fogod érezni: lassabb reakciók, akadozó multitasking és indokolatlan várakozási idők formájában.

A nehézség nem az, hogy nincs információ, hanem az, hogy nehéz jól értelmezni. A magszám, az órajel vagy a generáció önmagában nem mondja meg, milyen élményt ad majd a gép valós használat közben.

Ez az útmutató ebben segít. Nem konkrét modelleket sorol fel, hanem egy olyan gondolkodási keretet ad, amely mentén értelmezni tudod a különbségeket, és tudatos döntést hozhatsz.

1. Hogyan gondolkodj processzor választás előtt?

2. A döntés kiindulópontja: mire fogod használni?

3. Mit jelentenek valójában a CPU specifikációk?

4. Nem csak CPU-t veszel: platform

Számítógépház részei – így válassz jól PC házat

Ha PC építésen gondolkodsz, jó eséllyel már nézegetted a processzorokat, videokártyákat vagy memóriákat. A számítógépház viszont gyakran csak a végén kerül elő – „jó lesz valami szép”. Ez az a pont, ahol sokan hibáznak. A számítógépház részei ugyanis nemcsak esztétikai kérdést jelentenek, hanem konkrétan meghatározzák, mennyire lesz jól hűtött, csendes és bővíthető a géped. Egy rossz házban még a drága hardver is szenvedhet, míg egy jól megválasztott modell hosszú évekre stabil alapot ad. Ebben a cikkben végigvezetlek azon, mire figyelj, és hogyan hozd meg azt a döntést, amit később sem bánsz meg.

Miért nem mindegy, milyen számítógépházat választasz?

Számítógépház részei – az alapok, amiket mindenképp ismerned kell

A számítógépház váza és formátuma (form factor)

Belső elrendezés: hogyan hat a használhatóságra?

Hűtés és légáramlás – a teljesítmény kulcsa

Előlapi és felső csatlakozók (I/O panel)

Anyaghasználat és építési minőség

Dizájn és extra funkciók – csak látvány vagy valódi érték?

Hogyan válaszd ki a számodra ideális számítógépházat?

Gyakori hibák számítógépház választáskor

FAQ – Gyakori kérdések a számítógépház részeiről

Konklúzió

Miért nem mindegy, milyen számítógépházat választasz?

Sokan itt rontják el először: azt go

Számítógépház méretek: ATX, mATX vagy mini-ITX?

Egy új PC építésénél sokan a processzorral vagy a videokártyával kezdik – teljesen érthető módon. A számítógépház viszont gyakran csak a végén kerül szóba, pedig valójában az egész rendszer alapját határozza meg. Ha rosszul választasz, könnyen belefuthatsz olyan problémákba, mint a be nem férő videokártya, rossz hűtés vagy korlátozott bővíthetőség. A „számítógépház méretek” kérdése tehát messze nem csak arról szól, hogy mekkora doboz fér el az asztal alatt. Sokkal inkább arról, hogy mennyire lesz rugalmas, jól hűthető és jövőálló a konfigurációd. Ebben a cikkben végigvezetlek azon, hogy mit jelentenek valójában az egyes méretek, és hogyan tudsz olyan döntést hozni, amit később sem bánsz meg.

Mit jelent a számítógépház méret?

Számítógépház méret vs alaplap form factor – nem ugyanaz

A három fő alaplap szabvány röviden: ATX, mATX és mini-ITX

Ház típusok: mini tower, mid tower, full tower

Méretek és kompatibilitás – mi fér bele valójában?

Bővíthetőség és jövőállóság

Hűtés és airflow – a méret hatása a hőkezelésre

Méret vs teljesítmény – tényleg van különbség?

Ár és költségek – rejtett különbségek

Melyik méret kinek való? – döntési útmutató

Gyakori hibák számítógépház választásnál

Gyakran ismételt kérdések

Konklúzió

Mit